# A case for parallel-first languages in a post-serial, accelerated world

Paul Sathre Research Software Engineer Synergy Lab & NSF Center for Space, High-Performance and Resilient Computing Virginia Tech

### Disclaimers

- Imperfect tools are better than no tools, and doing serious science with them should be lauded, even as we strive to make better ones.

- Critical feedback does not diminish the value that prior art has given us

- All thoughts and opinions expressed are my own, and shouldn't be attributed to my employer, coworkers, or sponsors

- Logos and product names belong to their respective rights holders, and are neither an endorsement of this talk, nor of the referenced products

### My Background $\rightarrow$ portable accelerated computing

- Undergrad: •

- Went in with a high-end desktop for "course work"

- Quad-core 64-bit AMD, NVIDIA 8800 Ultra GPU, Aegia PhysX physics processing unit (PPU)

- Roadrunner just coming online  $\rightarrow$  friends & lab with PlayStation 3s

- Brief stint doing bioinformatics on Tilera Tile64

- GPGPU via OpenCL  $\rightarrow$  two summers at LANL (cosmo + neutron transport) OpenCL

- Grad school and shortly post-MS: CUDA ↔ OpenCL Interop

- MS Thesis: CUDA to OpenCL translation → (CU2CL) on NVIDIA GTX 480

- Interoperable MPI+{CUDA, OpenCL, OpenMP} for Micro-Air Vehicles  $\rightarrow$  (*MetaMorph*) Morph

- Running on Nvidia GPU, AMD GPU, Intel MIC, respectively

- Since then: languages and tools for *modern* heterogeneous HPC

- OpenCL support for FPGA: Linters (*FLOCL*) and autogenerators (*MetaCL*)

- SYCL for irregular apps: AMD+NVIDIA GPU (via AdaptiveCpp), Intel FPGA (via DPC++)

- GPU Chapel for irregular apps: perf./prod. tradeoffs  $\rightarrow$  partitionability  $\rightarrow$  portability (soon)

FLO

Meta-

### What I really care about:

Closing the gaps between the parallel hardware we already have, and the people who could benefit from it

### So how do we **enable** them? (Conversely, what are the **barriers** to use?)

## Setlist

- Intro [you are here]

- Act I: Parallelism is everywhere, start acting like it

- Act II: The rise of GPUs, up through today

- Act III: Chapel's role in our GPU future, and our role in Chapel's

- Outro

### ChapelCon #1: Looking back on ten CHIUW keynotes

- GPGPU was already in mind at CHIUW #1

- Python (and later Jupyter) interactive dev flows are important

- Keep turns within the human thought loop, whether compilation or analysis

- Need a middle ground between FAANG-scale frameworks which often don't scale down well, and laptop-scale which often don't scale up well

- Analysis, Viz, Packaging, *community-alignment* are all important

- PGAS tends to beat explicitly-distributed when it comes to network-perf and productivity

- Flexibility and performance are more important than transparency

- Start high level, but keep access and provide a smooth ramp to greater complexity

## Act I

### Parallelism is everywhere, start acting like it

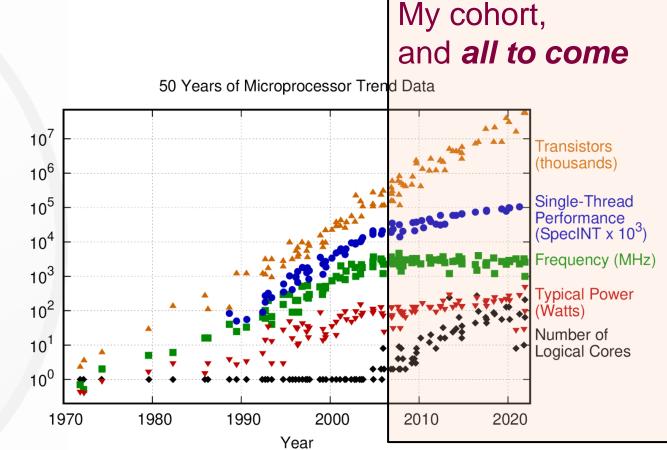

### Hardware is parallel, and likely to stay so

- Serial performance has barely improved since I started

- Parallel hardware was already common, now ubiquitous

- Try to buy a laptop or cellphone without at least dual-core

- HPC has been using parallel and distributed software, but it's still not very general

- Hardware is also *heterogeneous*, more on that in Act II

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batter New plot and data collected for 2010-2021 by K. Rupp

CC-by-4.0: https://github.com/karlrupp/microprocessor-trend-data/blob/master/50yrs/50-years-processor-trend.png

synergy.cs.vt.edu

Sathre, P. "A case for parallel-first languages in a post-serial, accelerated world" ChapelCon'24 -- June 7, 2024 HPC moved to parallel, distributed, and heterogeneous long ago

### But *nobody starts programming on an HPC cluster* They start on a laptop/desktop

So what are *regular users* using?

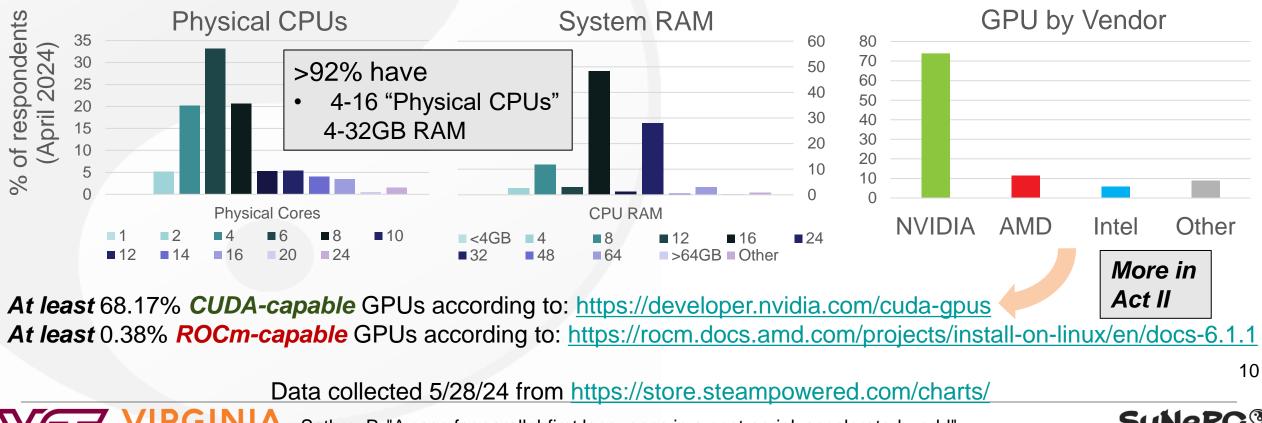

### What do desktop and laptop users actually have?

Steam hardware survey  $\rightarrow$  rough proxy for general-purpose users

– In reach of {hobbyists, tinkerers, undergrads} → future HPC buyers

Sathre, P. "A case for parallel-first languages in a post-serial, accelerated world" ChapelCon'24 -- June 7, 2024

### HPC is changing, broadening

- Users and developers are more mobile/remote

- Less cubicle high-power workstation, more laptop / BYOD / tablet / cell

- Are centrally-installed dev environments still the norm? Or more individual?

- Multicore + GPU at home in gaming / streaming / editing rigs

- Everybody's a Twitch, YouTube, insert-platform-here star

- It's not just the privately-owned datacenter anymore → lots of laaS

- Renting cycles as needed vs. surpassable Big Iron cap-ex

- Anyone with a credit card can buy GPU cycles for AI, crypto, etc.

- Need a *unified* approach to programming *all of it*

- CPUs, GPUs, NICs, and whatever comes next

### So regular users have (or can get) parallel hardware

### But isn't *parallelism* hard to understand?

### The natural order of the world is massively parallel!

- Humans have innate experiences and understanding of parallel processes

- Beehives  $\rightarrow$  Scatter/Gather

- School of fish, flock of sheep  $\rightarrow$  single instruction (sheepdog), multiple thread (sheep)

- Check-out lines → task parallelism and work stealing

- Road networks  $\rightarrow$  numerous parallel and sync constructs

Pipelined Parallelism (SIMD *LANES*)

Memory Fence (toll *STORE*)

### Semaphore (controlled intersection)

13

Images CC-by-2.0 (cropped): https://commons.wikimedia.org/w/index.php?curid=71040887,

https://www.flickr.com/photos/16801915@N06/19022810042,

https://www.flickr.com/photos/193316968@N06/52086734514

A Sathre, P. "A case for parallel-first languages in a post-serial, accelerated world"

ChapelCon'24 -- June 7, 2024

#### We have broad access to parallel hardware

# Humans experience *parallel phenomena* in their day-to-day lives

#### Why does it still seem **so hard**?

# Because we teach *serial first*, through the lens of old, *post-serial* norms!

### Reality and hardware are parallel, so teach that

- Even "serial" threads don't run in isolation

- OS time-slicing, async IO, ISP/power outages

- Teach how to be safe and effective in a *parallel world*

- New driver → defensive driving

- − New programmer → thread-safety and fault-tolerance

- After C/systems sequence, as an elective is too late → serial habits already anchored

- To move earlier, need a language that is easy, *parallel-first,* and *general*

- PGAS is more approachable for learning *distributed*

- Just some "further" cores/mem with more latency and failure modes

- Don't snail-mail a co-located co-worker! Use a whiteboard, post-its, Kanban, *lunch meeting*

https://www.flickr.com/photos/36989019@N08/22906552924

"Life is what

happens to-

you while

you're busy

making

other plans"

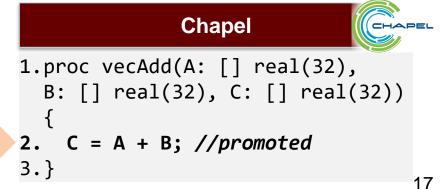

### Post-serial or "serial with sprinkles"

- Dominant programming models are still post-serial

- "Sprinkles": optional libraries, pragmas, language extensions

- Chapel presents a different option: *parallel-first* A non-separable part of the *keywords*, *data abstractions*, and *semantics* of the language (i.e. **promotion**)

- Why *parallel-first* matters?

- Philosophical: *realign* languages to hardware, *demystify* parallelism

- Technical: better ground-up *parallel safety* built into its fabric

- Technical: no conflicts between base and parallel sprinkle, they grow together

- ISO/IEC 14882:2011, *Information T*.

This OpenMP API specification refe of the OpenMP specification are exp may result in unspecified behavior.

OpenMP. 5.0 spec. (2018) 16

Sathre, P. "A case for parallel-first languages in a post-serial, accelerated world" ChapelCon'24 -- June 7, 2024

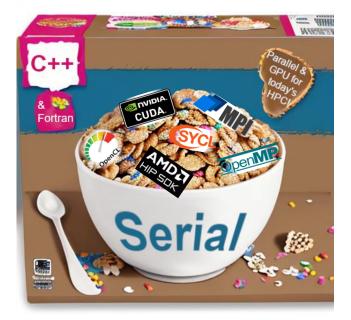

### Code Example: CPU vector add

#### Serial C

```

1.void vecAdd(float *A, float *B,

float *C, int n) {

2. for (int i=0; i<n; i++) {

3. C[i] = A[i]+B[i];

4. }

5.}</pre>

```

A vector is just a *linear collection of things*.

Should we express our code according to an *individual element's* experience?

```

OpenMP

1.#include <omp.h>

2.void vecAdd(float *A, float *B,

float *C, int n) {

3. #pragma omp parallel for

shared(A, B, C) private(i)

3.

4. for (int i=0; i<n; i++) {

4.

C[i] = A[i] + B[i];

5.}

5.

6. }

7.}

Or do we actually care

about the collective?

```

This is closer to the mental model

```

Chapel (without promotion)

```

```

1.proc vecAdd(A: [] real(32),

B: [] real(32), C: [] real(32))

{

2. forall i in C.domain {

3. C[i] = A[i] + B[i];

4. }

5.}

```

### Intermezzo

- The world and modern hardware are parallel, *let's start acting like it*

- Use parallel-first languages, and *teach them to new users*

- Move our mental model from "The Hero [thread]'s Journey", to "shepherds of threads"

- But we also have to think about *heterogeneous parallelism...*

## Setlist

- Intro

- Act I: Parallelism is everywhere, start acting like it

- [you are here]

- Act II: The rise of GPUs, up through today

- Act III: Chapel's role in our GPU future, and our role in Chapel's

- Outro

# Act II

### The rise of GPUs, up through today

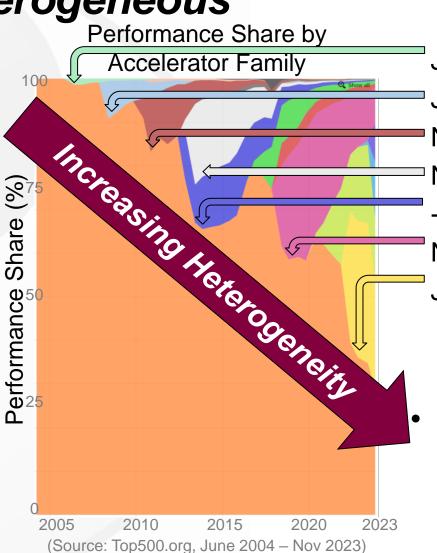

### Hardware is *heterogeneous*

- Heterogeneous hardware is ubiquitous (and has been)

- {floating-point-, graphics-, physics-, signal-, crypto-, tensor-, data-, vision-, reconfigurable-, ...}

Processing Units

- Some get married to the CPU as a SoC, some don't

- NVIDIA Grace Hopper, AMD MI300A APU, AMD Versal FPGA, Altera Agilex FPGA, etc.

June 2006: Clearspeed (1.4%)

June 2008: IBM Cell (8.6%)

Nov. 2010: NVIDIA Fermi (12.7%)

Nov. 2013: Intel Xeon Phi (17.7%)

+ NVIDIA Kepler (12.2%)

Nov. 2018: NVIDIA Volta (23.7%)

June 2022: AMD MI250 (30.2%)

Accelerator *du jour* keeps shifting vendor & language

SyNeRG synergy.cs.vt.edu

### Hardware is *heterogeneous*

- Accelerator *du jour* keeps shifting vendor & language

- Portable languages

necessary to reach

everything and reduce

rework!

November 2023: **70.1% GPU**

By vendor:

- NVIDIA: 36.3%

- Ampere: 14.3%

- Hopper: 12.9%

- Volta: 8.2%

- AMD: 24.9%

- MI250: 24.9%

- Intel: 9.0%

- Max Data Center: 8.9%

- No Coprocessor: 28.8%

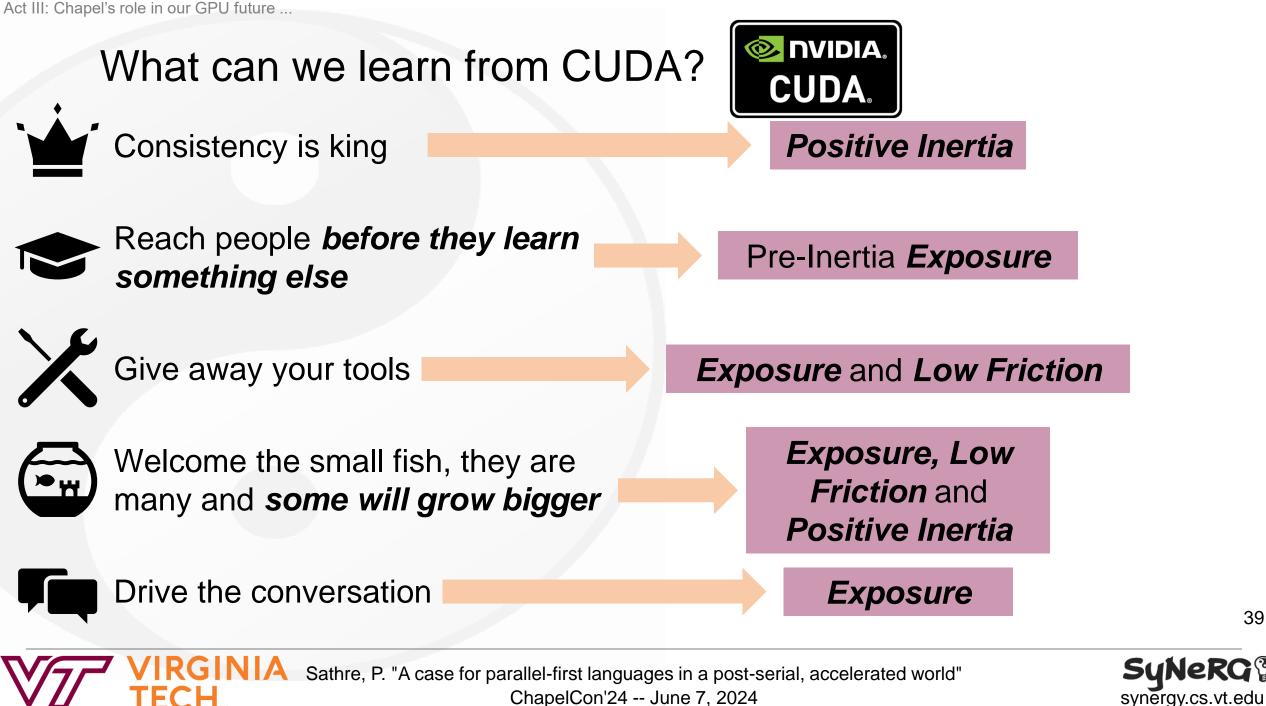

### What can we learn from CUDA?

- Consistency is king

- Pick a model, stick to it, and iterate on it when needed

- Build and keep knowledge: docs, forums, code examples

- Dead links are dead ends, insights lost to time

#### Reach people before they learn something else

University programs – free training and GPUs – were a smashing success

Give away your toolsEasy to install and use everywhere

Welcome the small fish, they are many and some will grow bigger

New codes, users, buyers start on laptops before growing to datacenter

#### Drive the conversation

Know where you excel, and show it to people

Sathre, P. "A case for parallel-first languages in a post-serial, accelerated world" ChapelCon'24 -- June 7, 2024

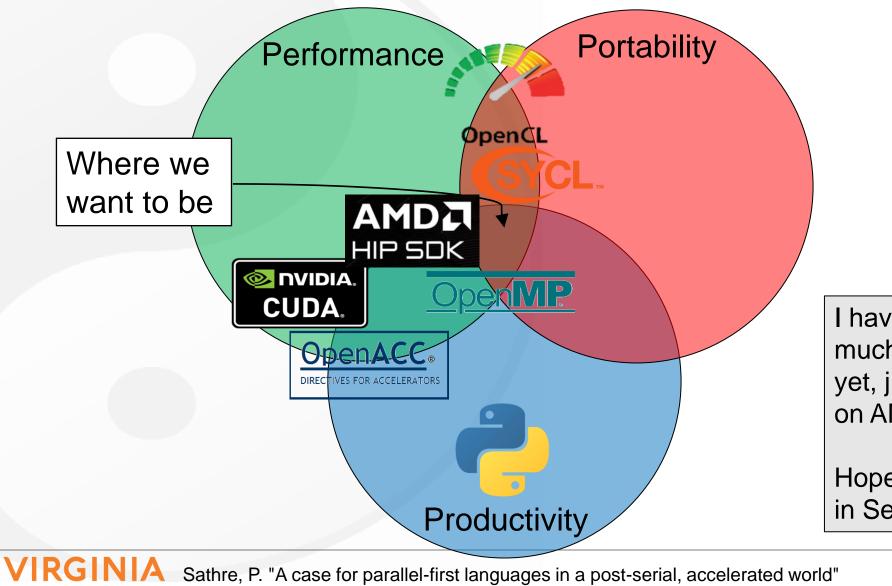

### GPU languages have a pick 2 of 3 problem

ChapelCon'24 -- June 7, 2024

I haven't gotten to do much portability work yet, just a few spot tests on AMD RDNA3 GPU.

```

Hope you saw the talks in Session #2!

```

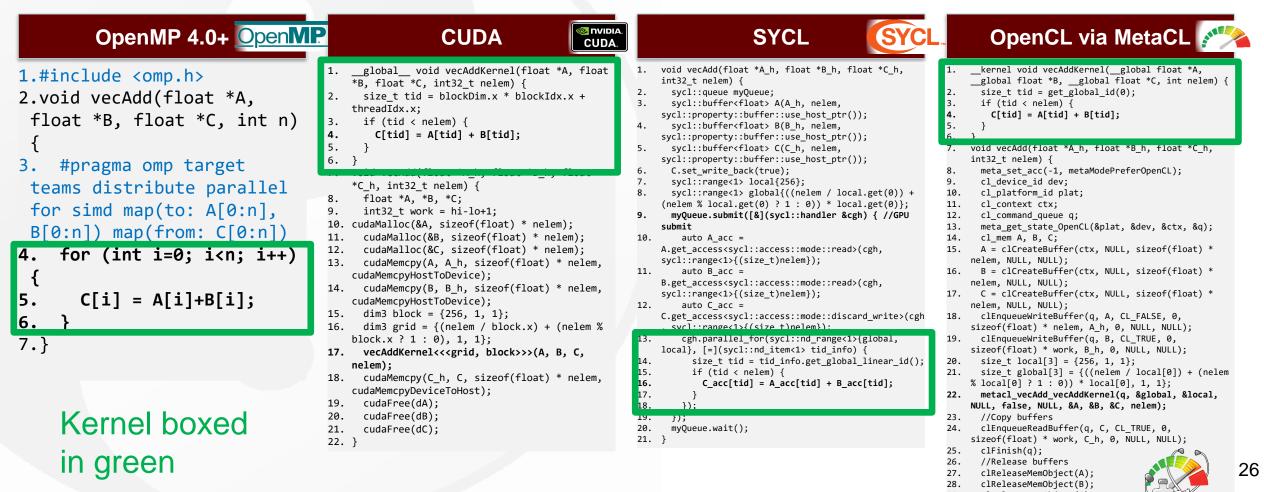

### **GPU Productivity Example: Vector Add**

• Either: concise but implicit or explicit but verbose

### Chapel GPU Productivity Example: Vector Add

- Chapel allows you to be **both** concise and explicit

- − Concise → Productivity Explicit → Maintainability

#### Chapel

#### 1.use GPU;

```

2.proc vecAdd(A_h: [] real(32), B_h: [] real(32), C_h: [] real(32)) {

on here.gpus[0] {

//enter 0-th device scope

3.

4. var A: [A_h.domain] real(32) = A_h; //copy-init from host

5. var B: [B_h.domain] real(32) = B_h; //copy-init from host

6. var C: [C h.domain] real(32) = noinit; //alloc without init

APEL

7. C = A + B;

//PROMOTED GPU add

8. C h = C;

//copy-from

9.

}

//release mem at GPU scope end

10.}

```

#### Kernel boxed in green

ΓΕϹΗ

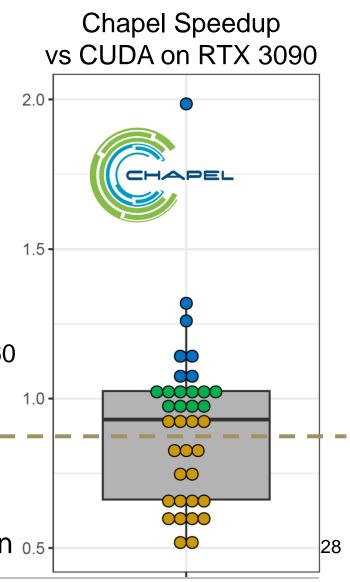

### Chapel GPU on Irregular Apps

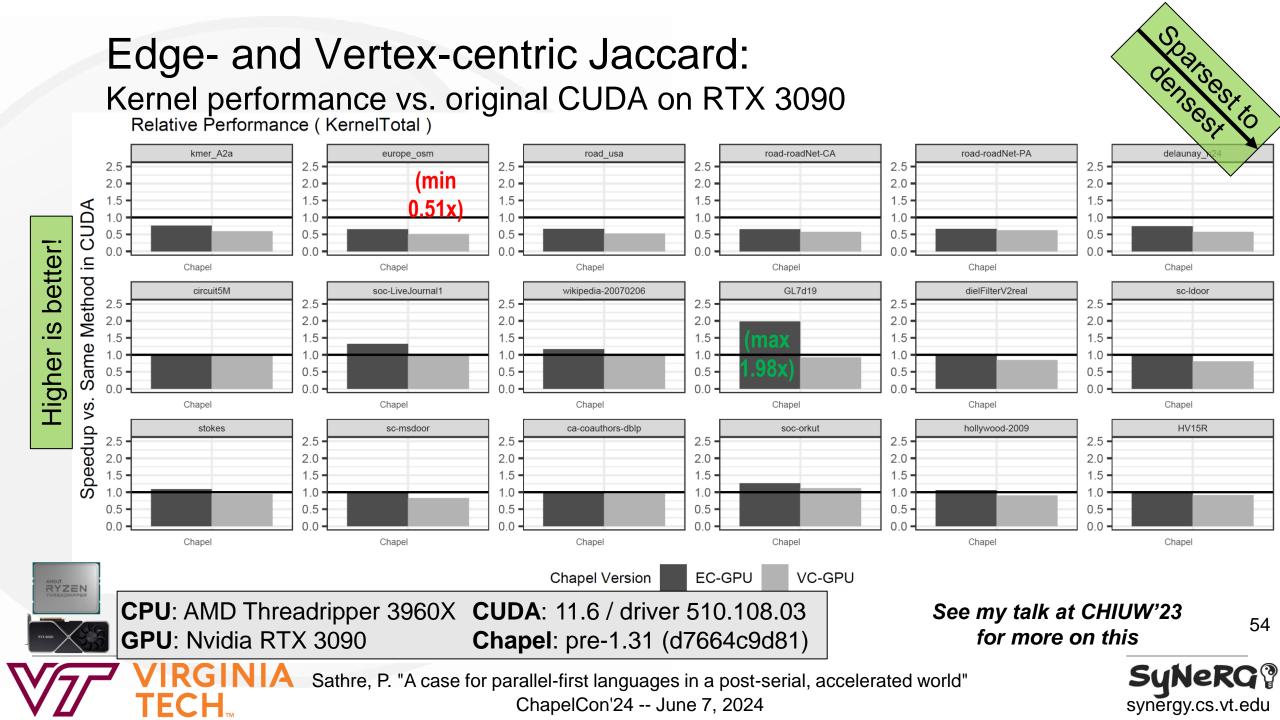

- Transliteration of CUDA Edge- and Vertex-centric graph analysis pipeline → Jaccard Similarity

- See my CHIUW'23 talk for more detail

- Non-trivial: 3D kernels, atomics, random-access

- Most recent line counts: CUDA 1212 vs Chapel 599 (-51%!!)

Relative kernel performance was great!

- 18 graph inputs (see appendix): |E| =~3-500M, avg. density:= ~2.1-160

- Min: 0.51x, Max: 1.98x, Geo. Mean: 0.87x

- Performance gap on the sparser inputs

- Performance parity ( $\pm$  5%) on the denser inputs

- Performance gain on a handful!

- Currently working on partitionable multi-GPU, multi-locale version 0.5

Sathre, P. "A case for parallel-first languages in a post-serial, accelerated world" ChapelCon'24 -- June 7, 2024

synergy.cs.vt.edu

$JS(D,F) = \frac{D \cap F}{r}$

G

### As a language for GPGPU kernels, Chapel is pretty good!

More *productive*, more *maintainable*, similar (and *improving*) *performance*

But how are people actually using GPGPU?

VIRGINIA Sathre, P. "A case for parallel-first languages in a post-serial, accelerated world" ChapelCon'24 -- June 7, 2024

Act II: The rise of GPUs...

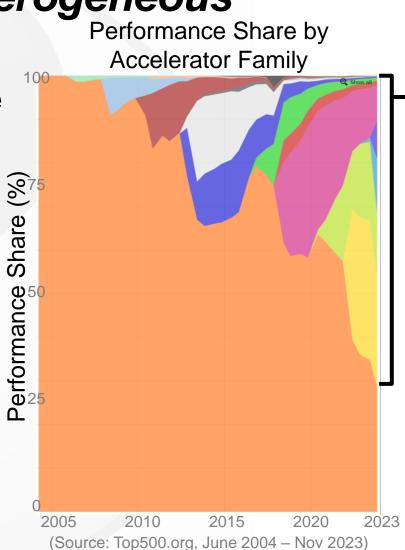

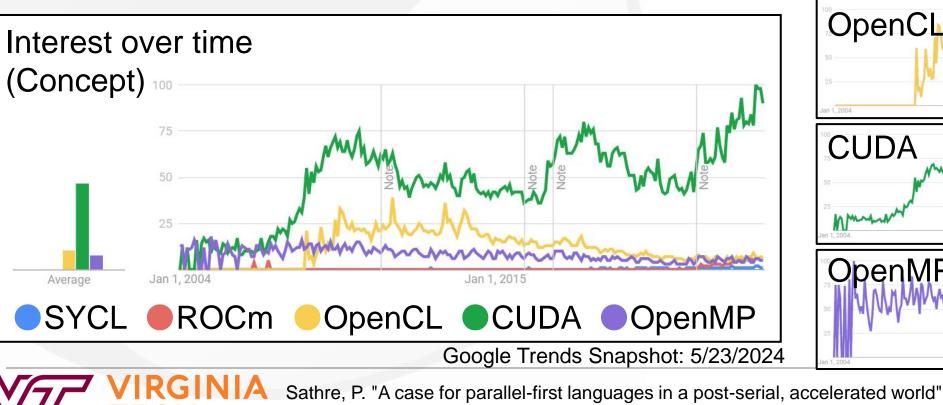

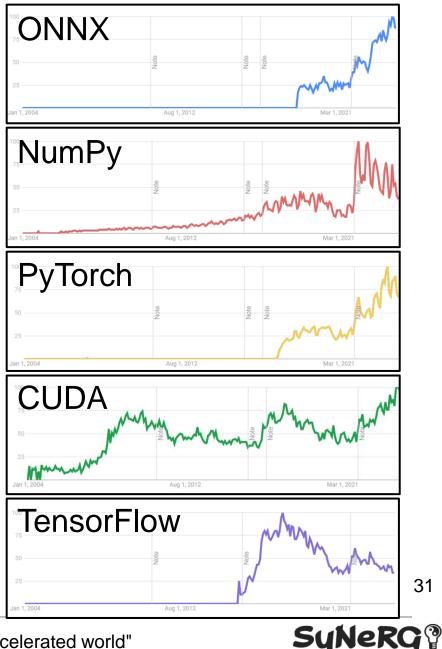

### Is it post-serial GPGPU languages?

- CUDA clearly the market leader

- OpenMP and OpenCL on the decline

- ROCm and SYCL on the rise

ChapelCon'24 -- June 7, 2024

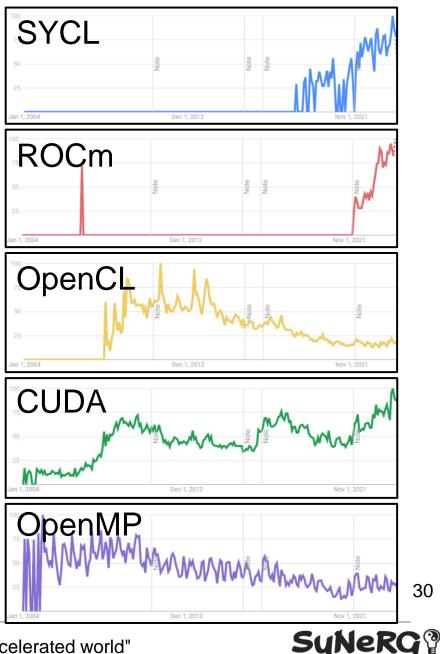

### Or is it Python with Libraries?

- High-performance Python → NumPy, et al

CuPy for GPU w/ compatible API is new, but growing

- TensorFlow & PyTorch compete w/ CUDA

- ONNX is following trends, but w/ lower share

### Intermezzo

- GPUs are critical to modern performance, both at exa- and laptop scales

- Chapel's GPU support is young but productive, performant and portable

- High-level Python has more *energy* & *interest* than low-level GPU

AI / Data science communities → new *federated* frontiers for HPC

- Chapel with GPU could *fill the gap* between *library-driven* Python and existing *post-serial* GPU languages!

## Setlist

- Intro

- Act I: Parallelism is everywhere, start acting like it

- Act II: The rise of GPUs, up through today

- [you are here]

- Act III: Chapel's role in our GPU future, and our role in Chapel's

- Outro

# Act III

### Chapel's role in our GPU future, and our role in Chapel's

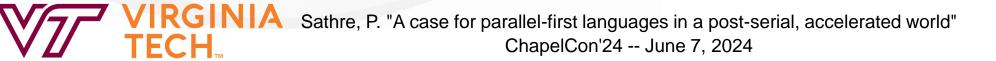

### A very simplified view of AI & Data Science

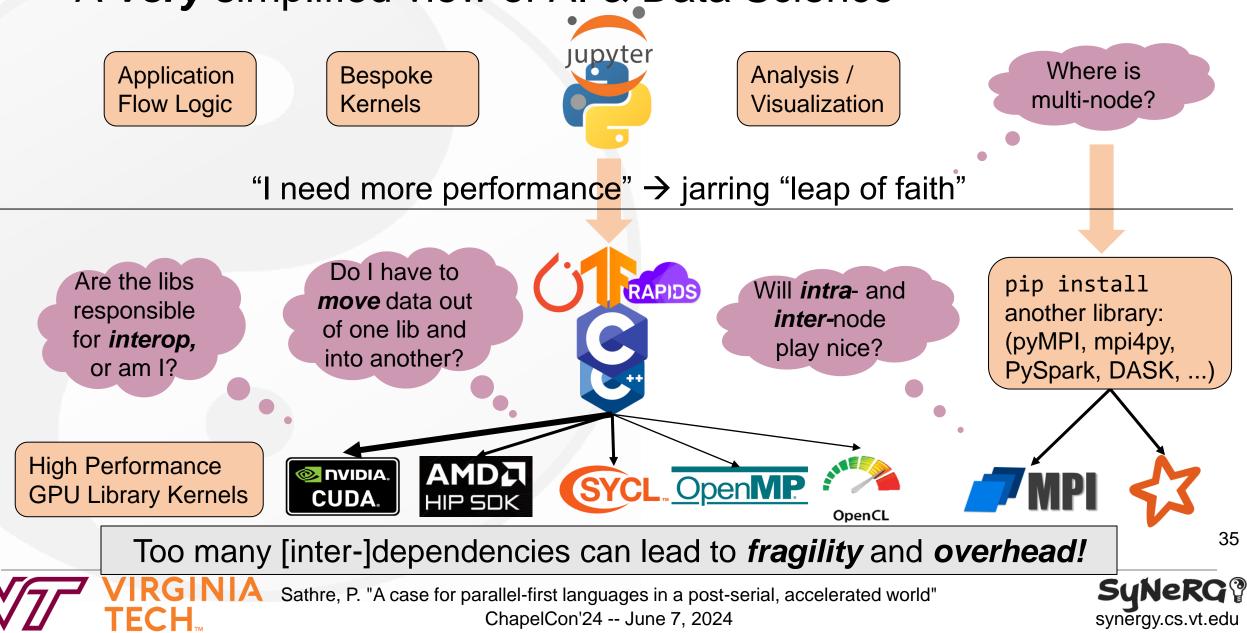

### Chapel eases path to parallel/GPU/distributed

## Available parallel and GPU Hardware ✓

## Parallel-first, *portable* GPU Language ✓

## AI and Data Science *energy* towards GPU ✓

## So what is still in Chapel's way? Inertia \* Friction \* Exposure

A Sathre, P. "A case for parallel-first languages in a post-serial, accelerated world" ChapelCon'24 -- June 7, 2024

Synerg

# Getting from A to B $\rightarrow$ $x_t = x_0 + t^* v_0 + t^2 a_0/2$

- Inertia (Position → *language share*)

- Old codes & langs are *battleships*: big, expensive, *powerful*, moved by committee

- Transliteration is necessary to "prove it works" but high effort relative to reward

- Friction (Velocity → rate of new codes)

- Programming is not just about the code, *it's about the whole ecosystem!*

- Installation, editor tooling, documentation, debugging, support forums, visualization, ...

- Ecosystem ease of use can help or hinder adoption

- Familiar workflows must be *trivial to reproduce*, or better yet, *improved upon*

- Exposure (Acceleration → rate of change in rate of new codes)

- The *earlier* and *more broadly* you can reach people, the better

- Users' *struggles* will identify friction points, and *successes* will feed excitement loop!

Act III: Chapel's role in our GPU future ...

#### How are we really doing on these?

VIRGINIA Sathre, P. "A case for parallel-first languages in a post-serial, accelerated world" ChapelCon'24 -- June 7, 2024

#### **Progress on Inertia**

- We're building on lessons from post-serial giants

- Not going anywhere, but we grow as a complement to them

- Higher-level for most, dip into post-serial via interop when needed

- Year-over-year we've increased breadth and depth of Chapel codes – Most successes are from new codes and users, not transliteration!

- Rigorous, at-scale successes are slowly chipping away

- I think it wins on clarity for maintainability, but I'm not sure there's enough ulletChapel-native developers for a robust HR ecosystem (yet)

- It's not just the code, it's the availability of people who know how to work on it

New codes and

### **Friction points**

#### Check out Session #1!

- 2.0 improved stability, docs, diags.! Work ongoing on LSP tools, debugging, interactivity

- *"Where .exe?"* Need better install, migration, *in situ* viz → where is our matplotlib?

| Approach             | Deb package? 🧲 | GPU? Portability?      | From source?  | New compiler?     |

|----------------------|----------------|------------------------|---------------|-------------------|

| <u>Open<b>MP</b></u> | Yes            | Optional               | No            | No                |

| <b>MPI</b>           | Yes            | Advanced only          | Advanced only | Yes               |

| CUDA.                | Yes            | NVIDIA required        | No            | Yes               |

| AMDA<br>HIP SDK      | Yes w/ Repo    | AMD or NVIDIA required | No            | Yes               |

| OpenCL               | Yes            | Optional               | No            | Host No, Dev. Yes |

| SYCL. OneAPI         | Yes w/ Repo    | Optional               | No            | Yes               |

| SYCL AdaptiveCpp     | No             | Optional               | Yes           | Yes               |

| CPU/single-loc       | Soon!!         | No                     | No            | Yes               |

| GPU/multi-loc        | No             | Optional AMD or NVIDIA | Yes           | Yes               |

42

Sathre, P. "A case for parallel-first languages in a post-serial, accelerated world" ChapelCon'24 -- June 7, 2024

#### What about Exposure?

- We're here, so how'd we get here? → Community survey might show common themes

- *Curricula* are the long term answer, but *generality* is a precursor!

- Right now part of *inertia*: slow battleships only moved by committees

- But there are other places to teach: bootcamps, pre-college, online platforms!

- $3^{rd}$  party blogs are **great**  $\rightarrow$  independent credibility

- Increased social media needs to align to where prospective users *already are*

- There's a ton of CS, AI, Python, Rust, ProgrammerHumor on Reddit, but r/Chapel is quite thin

- Need to reach *beyond* HPC bastions, because *everyone* has parallel hardware now

- Instead of "pushing out" from HPC spaces, "pull in" concepts and people from more general spaces

43

Check out

Luca's talk next

in Session #3

#### Where to put our efforts? -> Cascades start upstream

Sathre, P. "A case for parallel-first languages in a post-serial, accelerated world" ChapelCon'24 -- June 7, 2024

- *Inertia* is a giant / battleship, strong and slow

- Small splashes won't move it, but riding a tide could → GPGPU!

- *✓**✓**Friction* **is a solvable engineering problem**

- Make moving to Chapel as easy as drifting downstream

- Programmers we've reached have *interest* and *energy* that we shouldn't *waste on turbulence*

- 2.0 stability, LSP tools, *installation*, interactivity, debugging, *visualization*

- *Exposure* is important, but not a guarantee!

- AI / data science devs are gravitating to more general languages

- Reach into general spaces to show a better path downstream

- Focusing on the *upstream experience* and *potential energy* of newer users, could finally shift the tide to *parallel-first*

*Cascades in winter* Photo Credit: Paul Sathre, 2015

Outro

- The real world and everyday hardware are parallel, so lets act like it

- Use *parallel-first* languages, like Chapel and *teach them to new users*

- Chapel's GPU support learned quickly from prior GPU approaches

- Now a productive, performant, and portable contender

- Let's align to broader GPU trends towards a future in AI / Data science

- Smooth the gap between high-level libraries, and low-level post-serial

- To grow a Cascade, seek *general* users & provide a *low-friction* experience

Reduce barriers to entry, expand reach from HPC to *general parallelism*

#### Thanks

- ... to current members and alums of Synergy Lab @ VT

- ... to the Chapel team at HPE for Q&A, feature requests, discussion

- … and inviting me to speak today!

- Particular shoutouts to GPU and IO teams: Brad, Engin, Andy, Ben H., Michael, Lydia

- ... to the Chapel community for fighting hard on inertia, exposure, and friction

- Sponsorship

- The work detailed herein has been supported in part by NSF I/UCRC CNS-1822080 via the NSF Center for Space, High-performance, and Resilient Computing (SHREC).

46

Sathre, P. "A case for parallel-first languages in a post-serial, accelerated world" Synercy.cs.vt.edu

#### **Question & Answer**

- The real world and everyday hardware are parallel, so lets act like it

- Use *parallel-first* languages, like Chapel and *teach them to new users*

- Chapel's GPU support learned quickly from prior GPU approaches

- Now a productive, performant, and portable contender

- Let's align to broader GPU trends towards a future in AI / Data science

- Smooth the gap between high-level libraries, and low-level post-serial

- To grow a Cascade, seek *general* users & provide a *low-friction* experience

Reduce barriers to entry, expand reach from HPC to *general parallelism*

VIRGINIA Sathre, P. "A case for parallel-first languages in a post-serial, accelerated world" TECH

## **Encore Slides**

VIRGINIA Sathre, P. "A case for parallel-first languages in a post-serial, accelerated world" ChapelCon'24 -- June 7, 2024

SyNerg

### **Difficult Discussion Questions**

- If a business has a Chapel-driven product or internal tool, how quickly can they bring a new grad up to speed to work on the language?

- If we use Chapel's higher-level parallelism for teaching, are we hiding parts of the underlying parallelism that are critical for developing deep understanding?

- After improving base language installation, what is our package ecosystem like? Is / could Mason be as easy as Pip, Cargo, etc.?

- How well and portably do we expose GPU features like threadfence, tensor cores?

- Is a new language more or less rigid than coding to a [large] C/++ framework?

### Wishlist

- Viz Viz Viz and Interactivity

- GPU-enabled install packages

- WSL for students, deb for me, rpm and laaS images for business

- Evangelism, show how good 2.0 is on real, important problems

- Tutorial series, in places where people are learning about code

- YouTube, Twitch, Reddit, Blogs?

- Installation all the way through to first GPGPU code

- Curricula examples for profs to grab-n-go

- Auto-grading plugin(s) via LSP?

- Automatically co-schedule forall/foreach to CPU+GPU(s)

- i.e. *not* an explicitly-partitioned cobegin

- Ok to start with strictly unified memory within a single locale

- Intel GPU support eventually  $\rightarrow$  3 competitors is good for user pricing

#### Select artifacts

- OpenDwarfs: <u>https://github.com/vtsynergy/OpenDwarfs</u>

- 13 computational idioms for OpenCL. Would love to see "Chapel-tastic" versions!

- CU2CL: <u>https://github.com/vtsynergy/CU2CL</u>

- MetaMorph: <u>https://github.com/vtsynergy/MetaMorph</u>

- MetaCL: <u>https://github.com/vtsynergy/MetaMorph/tree/master/metamorph-generators/opencl</u>

- Unpartitioned Chapel Jaccard

- CHIUW'23 Talk: https://chapel-lang.org/CHIUW/2023/SathreSlides.pdf

- Paper: <u>https://chapel-lang.org/CHIUW/2023/Sathre.pdf</u>

- Code: <u>https://github.com/vtsynergy/Chapel-Examples</u>

- Input data: https://chrec.cs.vt.edu/SYCL-Jaccard/HPEC22-Data/index.html

- Other lab code: <u>https://github.com/vtsynergy</u>

- And papers: <u>https://synergy.cs.vt.edu/publications.php</u>

- Points of contact: {sath6220, feng} at cs dot vt dot edu

## Code Example: GPU 3D vertex-centric Jaccard Similarity

## We did run into some issues porting a 3D CUDA kernel

- GPU foralls are only 1D (for now)

- Solution: Linearize loop range, then de->

- for-by loops do *NOT* GPU-ize (yet)

- Problem: non-constant by clause can halt

- Solution: Replace with while-count

- Accumulate via atomicAdd did NOT GPU-ize before Chapel 1.31

- Solution: Call CUDA's via extern C

- Now has a gpuAtomic<Func> API

- Could *incrementally validate* as kernels were transparently mapped to CPU

#### See my talk at CHIUW'23 for more on this

NVIDIA

var intersect : [0..<numEdges] real(32);</pre> forall id in srcIters\*destIters\*isectIters { var nd\_id : 3\*int = get\_ND\_ID(id); var zCount = nd id(2); while (zCount < srcIters) {</pre> var yCount = nd\_id(1); while (yCount < destIters) {</pre> var xCount = nd\_id(0); while (xCount < isectIters) {</pre> ... // bin-search fgpuAtomicAdd(intersect[writeAddr], 1.0); xCount += nd\_id.global\_dim(0); } yCount += nd\_id.global\_dim(1); } zCount += nd\_id.global\_dim(2); }

Sathre, P. "A case for parallel-first languages in a post-serial, accelerated world" ChapelCon'24 -- June 7, 2024 52

#### Sparsest to denses Edge- and Vertex-centric Jaccard: Data Sparsest/Largest **Smallest** Road-roadNet-CA **Road-roadNet-PA** Kmer A2a Europe osm Road usa Delaunay n24 Protein k-mers European roads US roads California roads Pennsylvania roads Random Triangulations V: 171M V: 50.9M V: 23.9M V: 1.96M V: 1.09M V: 16.8M E: 361M E: 108M E: 57.7M E: 5.52M E: 3.08M E: 101M & Avg: 2.82 **%** Avg: 2.11 & Avg: 2.12 & Avg: 2.41 & Avg: 2.83 & Avg: 6.00 Brange: 39 Std. Dev.: 0.56 ਰ Range: 12 ਰੋRange: 8 ਰੋRange: 11 ਰੋRange: 8 ਰRange: 23 <sup>0</sup> Std. Dev.: 0.48 Std. Dev.: 0.93 Std. Dev.: 0.99 Std. Dev.: 1.02 ⊔ Std. Dev.: 1.34 Gini Index: 0.055 Gini Index: 0.085 Gini Index: 0.211 Gini Index: 0.185 Gini Index: 0.188 Gini Index: 0.122 Soc-LiveJournal1 Wikipedia-20070206 **GL7d19** dielFilterV2real Sc-Idoor circuit5M Social network Web page links Voronoi differentials Dielectric resonator Large circuit Large door V: 952K V: 5.56M V: 4.85M V: 3.57M V: 1.96M V: 1.16M E: 54.0M E: 85.7M E 84.8M E: 41.5M E: 74.6M E: 47.4M & Avg: 38.2 & Avg: 9.71 & Avg: 17.7 & Avg: 23.8 & Avg: 40.9 & Avg: 43.6 o Std. Dev.: 1357 Range: 20.3K Std. Dev.: 16.1 ਰ Range: 188K ਰ Range: 134 ਰੋRange: 76 Std. Dev.: 255 Ճ Std. Dev.: 6.73 dStd. Dev.: 14.8 Gini Index: 0.711 Gini Index: 0.183 Gini Index: 0.577 Gini Index: 0.759 Gini Index: 0.088 Gini Index: 0.201 **HV15**R Stokes Sc-msdoor Ca-coauthors-dblp Soc-orkut Hollywood-2009 VLSI process sim. Medium Door Coauthorship Social network **Costarring Actors** CFD of engine fan V: 416K V: 2.02M V: 11.4M V: 540K V: 3.00M V: 1.14M E: 325M E: 18.8M E: 30.5M E: 516M E: 213M E: 113M & Avg: 45.1 & Avg: 56.4 & Avg: 71.0 & Avg: 98.9 <sup>®</sup>Avg: 161 & Avg: 45.1 Range: 1728 Trange: 3298 Range: 11.5K Range: 491 Range: 76 Range: 27.5K Std. Dev.: 66.2 ص Std. Dev.: 13.7 ص Std. Dev.: 140 Std. Dev.: 47.8 Gini Index: 0.166 Gini Index: 0.392 Gini Index: 0.544 Gini Index: 0.558 Gini Index: 0.750 Gini Index: 0.155 Graph data and images CC-BY-4.0 from the SparseSuite Matrix Collection (https://sparse.tamu.edu/). Densest 53

Preprocessed CSR binary files: https://chrec.cs.vt.edu/SYCL-Jaccard/HPEC22-Data/index.html

Sathre, P. "A case for parallel-first languages in a post-serial, accelerated world" ChapelCon'24 -- June 7, 2024

**FFC**

SyNeRG

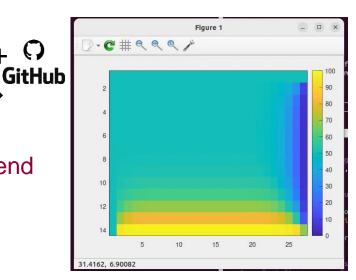

### {AI, Data, Domain} Scientists need visualization!

- Python/Jupyter drive an *interactive* code  $\rightarrow$  viz  $\rightarrow$  analysis loop

- Need to support visualization within the human thought loop to attract these workflows

- Chapel doesn't have a plotting module, but could C interop fill the role? "How hard can it be?"

- Experiment with Chapel  $\rightarrow C \rightarrow C++$  interop via matplot++ O

- 1024x512, 5-point stencil Jacobi heat diffusion toy, after 10k iters  $\rightarrow$

- ✓ 62 lines of Chapel application with 8 calls to library

- Grid subsampled to 26x13 *in a single line* for slow gnuplot backend

- ★ ... but 32 lines of manual Chapel→C binding

- not great, but could be automated via c2chape1

- **x** ... and 97 lines of manual  $C \rightarrow C++$  binding

- There is a gold mine of wrappable AI and Data Science libraries

- ... but would need both Chapel & C++ experience, rough otherwise

A Sathre, P. "A case for parallel-first languages in a post-serial, accelerated world" ChapelCon'24 -- June 7, 2024

Starting condition: 50° Boundary conditions: S=100, E=0, N&W=50 1-thick ghost padding55